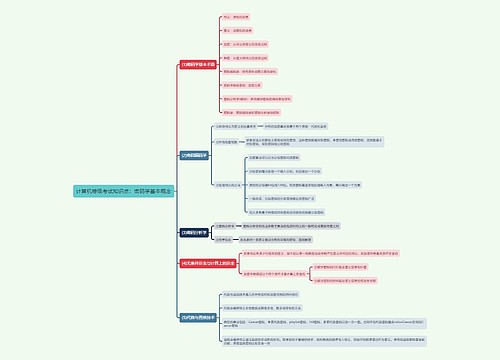

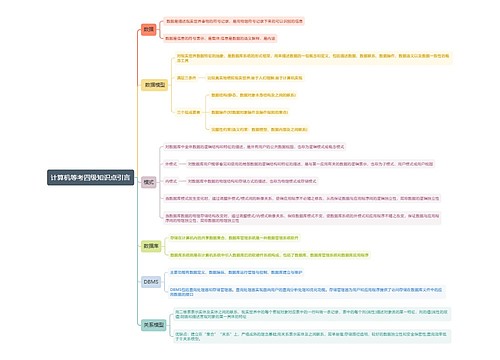

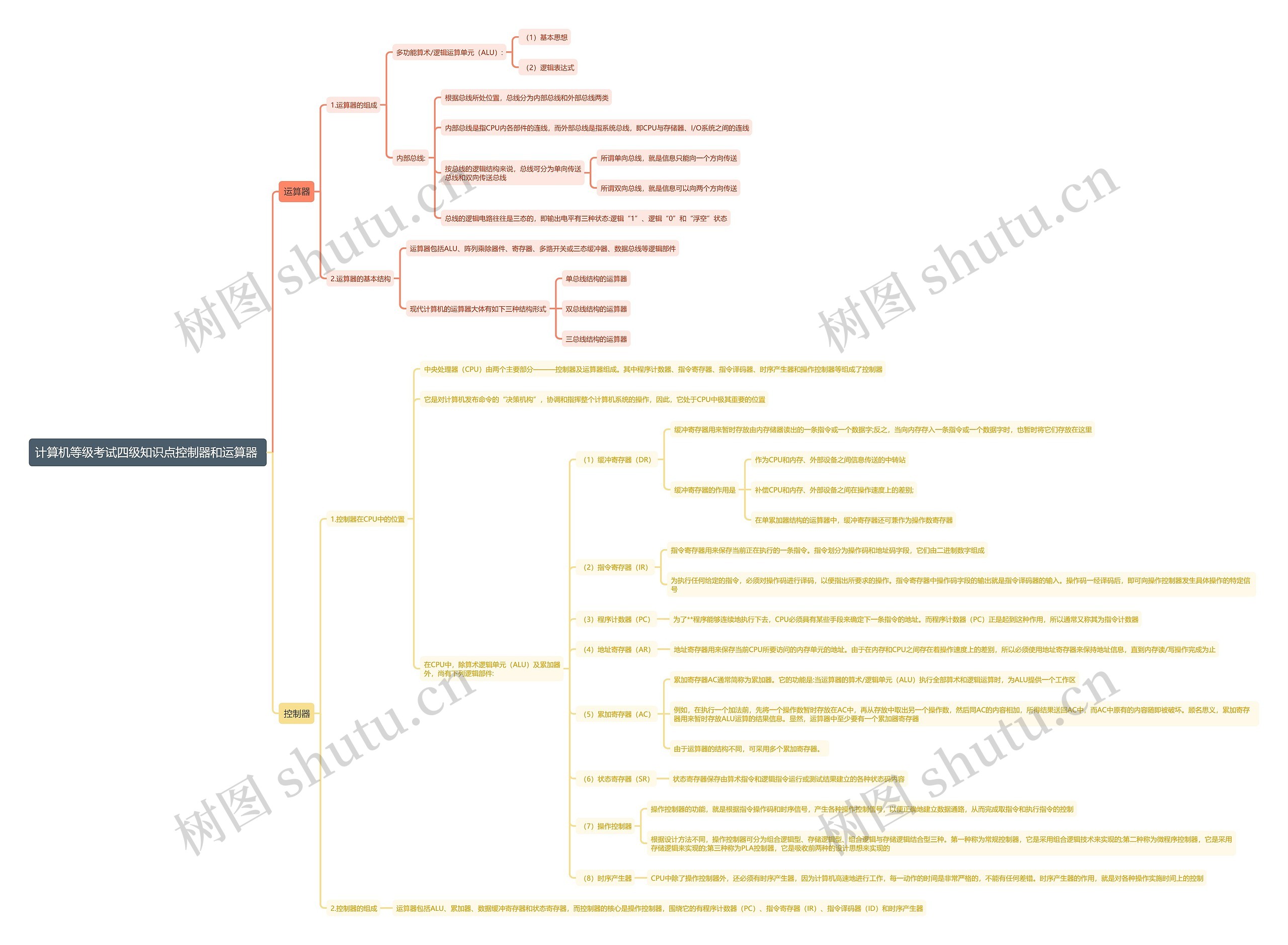

中央处理器(CPU)由两个主要部分———控制器及运算器组成。其中程序计数器、指令寄存器、指令译码器、时序产生器和操作控制器等组成了控制器

它是对计算机发布命令的“决策机构”,协调和指挥整个计算机系统的操作,因此,它处于CPU中极其重要的位置

在CPU中,除算术逻辑单元(ALU)及累加器外,尚有下列逻辑部件:

(1)缓冲寄存器(DR)

缓冲寄存器用来暂时存放由内存储器读出的一条指令或一个数据字;反之,当向内存存入一条指令或一个数据字时,也暂时将它们存放在这里

缓冲寄存器的作用是

补偿CPU和内存、外部设备之间在操作速度上的差别;

在单累加器结构的运算器中,缓冲寄存器还可兼作为操作数寄存器

(2)指令寄存器(IR)

指令寄存器用来保存当前正在执行的一条指令。指令划分为操作码和地址码字段,它们由二进制数字组成

为执行任何给定的指令,必须对操作码进行译码,以便指出所要求的操作。指令寄存器中操作码字段的输出就是指令译码器的输入。操作码一经译码后,即可向操作控制器发生具体操作的特定信号

(3)程序计数器(PC)

为了**程序能够连续地执行下去,CPU必须具有某些手段来确定下一条指令的地址。而程序计数器(PC)正是起到这种作用,所以通常又称其为指令计数器

(4)地址寄存器(AR)

地址寄存器用来保存当前CPU所要访问的内存单元的地址。由于在内存和CPU之间存在着操作速度上的差别,所以必须使用地址寄存器来保持地址信息,直到内存读/写操作完成为止

(5)累加寄存器(AC)

累加寄存器AC通常简称为累加器。它的功能是:当运算器的算术/逻辑单元(ALU)执行全部算术和逻辑运算时,为ALU提供一个工作区

例如,在执行一个加法前,先将一个操作数暂时存放在AC中,再从存放中取出另一个操作数,然后同AC的内容相加,所得结果送回AC中,而AC中原有的内容随即被破坏。顾名思义,累加寄存器用来暂时存放ALU运算的结果信息。显然,运算器中至少要有一个累加器寄存器

(6)状态寄存器(SR)

状态寄存器保存由算术指令和逻辑指令运行或测试结果建立的各种状态码内容

(7)操作控制器

操作控制器的功能,就是根据指令操作码和时序信号,产生各种操作控制信号,以便正确地建立数据通路,从而完成取指令和执行指令的控制

根据设计方法不同,操作控制器可分为组合逻辑型、存储逻辑型、组合逻辑与存储逻辑结合型三种。第一种称为常规控制器,它是采用组合逻辑技术来实现的;第二种称为微程序控制器,它是采用存储逻辑来实现的;第三种称为PLA控制器,它是吸收前两种的设计思想来实现的

(8)时序产生器

CPU中除了操作控制器外,还必须有时序产生器,因为计算机高速地进行工作,每一动作的时间是非常严格的,不能有任何差错。时序产生器的作用,就是对各种操作实施时间上的控制

U633687664

U633687664

~漫埗陽茪~

~漫埗陽茪~